- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

Эпитаксиальные слои: основа современных полупроводниковых устройств

Рисунок 1: Иллюстрирует корреляцию между концентрацией легирующих примесей, толщиной слоя и напряжением пробоя для униполярных устройств.

Подготовка эпитаксиальных слоев SiC в первую очередь включает такие методы, как выращивание методом испарения, жидкофазная эпитаксия (LPE), молекулярно-лучевая эпитаксия (MBE) и химическое осаждение из паровой фазы (CVD), причем CVD является преобладающим методом массового производства на заводах.

Таблица 1: Дает сравнительный обзор основных методов подготовки эпитаксиального слоя.

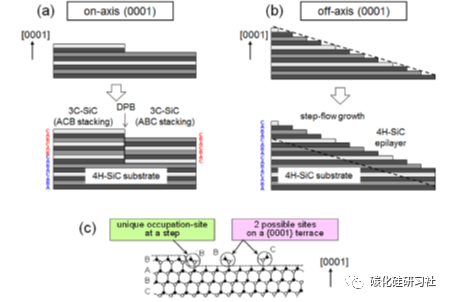

Новаторский подход предполагает выращивание на внеосевых подложках {0001} под определенным углом наклона, как показано на рисунке 2 (b). Этот метод значительно увеличивает плотность ступеней, одновременно уменьшая их размер, способствуя зародышеобразованию, прежде всего, в местах группировки ступеней и, таким образом, позволяя эпитаксиальному слою идеально повторять последовательность укладки подложки, исключая сосуществование политипов.

Рисунок 2: Демонстрирует физический процесс ступенчатой эпитаксии в 4H-SiC.

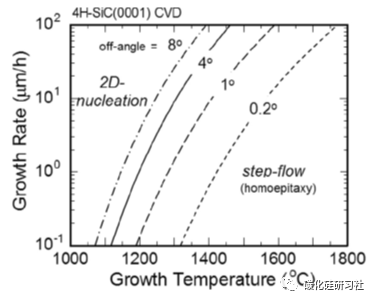

Рисунок 3: Показаны критические условия для роста CVD при ступенчатой эпитаксии 4H-SiC.

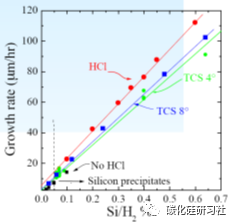

Рисунок 4: Сравнение темпов роста при различных источниках кремния для эпитаксии 4H-SiC.

В области приложений низкого и среднего напряжения (например, устройств на 1200 В) технология эпитаксии SiC достигла зрелой стадии, обеспечивая относительно превосходную однородность толщины, концентрации легирования и распределения дефектов, адекватно отвечая требованиям для SBD низкого и среднего напряжения. , MOS, устройства JBS и другие.

Однако область высокого напряжения по-прежнему представляет собой серьезные проблемы. Например, устройства, рассчитанные на напряжение 10 000 В, требуют эпитаксиальных слоев толщиной примерно 100 мкм, но эти слои имеют значительно меньшую толщину и однородность легирования по сравнению с их низковольтными аналогами, не говоря уже о пагубном влиянии треугольных дефектов на общую производительность устройства. Высоковольтные приложения, в которых предпочтение отдается биполярным устройствам, также предъявляют строгие требования к сроку службы неосновных носителей, что требует оптимизации процесса для улучшения этого параметра.

В настоящее время на рынке доминируют 4-дюймовые и 6-дюймовые эпитаксиальные пластины SiC с постепенным увеличением доли эпитаксиальных пластин SiC большого диаметра. Размер эпитаксиальных пластин SiC принципиально определяется размерами подложек SiC. Поскольку 6-дюймовые подложки SiC теперь коммерчески доступны, переход от 4-дюймовой к 6-дюймовой эпитаксии SiC неуклонно продолжается.

По мере развития технологии изготовления подложек SiC и расширения производственных мощностей стоимость подложек SiC постепенно снижается. Учитывая, что на подложки приходится более 50% стоимости эпитаксиальных пластин, ожидается, что снижение цен на подложки приведет к снижению затрат на эпитаксию SiC, тем самым обещая более светлое будущее для отрасли.**